MOS Technology 6510

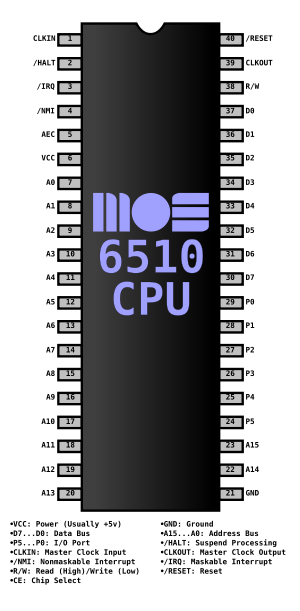

El MOS Technology 6510 es un microprocesador diseñado por MOS Technology, Inc., y es el sucesor directo del célebre 6502.

El principal cambio respecto del 6502 es la incorporación de un puerto de Entrada/Salida de 8 bits de propósito general (solo seis pines I/O están disponibles en la versión más común del 6510). Además, el bus de direcciones podía hacerse triestado.

El 6510 fue solo ampliamente usado en el ordenador doméstico Commodore 64 y, en cantidades significativamente más pequeñas, en el Commodore SX-64 (una versión portable del C64). En ambos casos los pines extra del procesador se utilizaron para controlar el mapa de memoria del ordenador, y en el C64, para controlar el motor eléctrico del Commodore Datassette, la lectograbadora dedicada de casete. Era posible, escribiendo la correcta máscara de bits al procesador en la dirección $01, mapear la totalidad de los 64K de RAM del C64, no dejando mapeados ni ROM ni puertos de entrada/salida.

Variantes

En 1985 MOS produjo el 8500, una versión HMOS del 6510. Aparte del cambio del proceso de fabricación, es idéntico a la versión NMOS del 6510. El 8500 se diseñó principalmente para utilizarlo en el Commodore 64C, una verión modernizada del C64 en carcasa tipo Commodore 128. Sin embargo en 1985, cantidades limitadas del 8500 se utilizaron en viejos C64 con base NMOS. Finalment hizo su aparición oficial en 1987, apareciendo en una placa base que utilizaba el nuevo chipset 85xx HMOS.

La variante 7501/8501 del 6510 se utilizó en los ordenadores domésticos Commodore 16, Commodore 116 y Commodore Plus/4, y el MOS Technology 8502, con capacidad de 2 MHz, se utilizó en el Commodore 128. Todas estas CPUs eran compatibles a nivel de instrucción (incluyendo las instrucciones no documentadas), excepto el 8502, donde se han encontrado diferencias en las instrucciones no documentadas.

La unidad de disco Commodore 1551 utiliza el 6510T, una versión del 6510 con ocho líneas de entrada/salida. Las señales NMI y RDY no están disponibles.

Componentes

Program Counter: Elemento que una vez proporcionada la primera instrucción, basta que sea incrementado en una unidad para que proporcione la dirección de la segunda instrucción.

Registros índices X e Y: Sirven para llevar a cabo un modo de direccionado, denominado indexado con el que la localización del operando de una instrucción se busca en la MEM añadiendo el contenido de estos registros a la dirección especificada en la instrucción.

Registro de Estados: Registro de 8 bits, 7 son significativos y sirven para señalar una situación provocada en la ejecución que se acaba de realizar.

Stack Pointer: Se trata de un contador programable que direcciona la página 1 de la MEM como si se tratase de una pila LIFO. Para simplificar la localización de las posiciones de MEM se lee la estructura en forma de páginas, cada una de las cuales consta de varias líneas o posiciones. Así, una MEM de 64K posiciones, se puede dividir en 256 páginas de 256 líneas cada una.

Bus de direcciones: Comprende las 16 líneas del bus de direcciones, de carácter unidireccional.

Bus de Datos: Consta de 8 líneas bidireccionales, por las que se transfieren los datos y las instrucciones, en sus salidas hay buffers amplificadores capaces de soportar una carga.

Características y Mnemotécnicos

A partir de un código creado en C para emular el funcionamiento se obtiene:

Definiendo los tipos word de tamaño de 16 bits (2 bytes) y byte (8 bits) Un struct cpu:

word cpu.PC, cpu.MAR byte cpu.A, cpu.X, cpu.Y, cpu.IR, cpu.SP, cpu.MBR, cpu.FLAGS

funciones "void":

memoria() cmp() fetch_dato() cpx() fetch_codigo() cpy() poner_dato() dec() fetch_dir() eor() carry() inc() negative() lsr() zero() pop() overflow() push() adc() rol() and() ror() asl() sbc() brach() cilco_ejec()

El switch (cpu.IR) contendrá 85 opcodes (codop) de los 256 disponibles (0..255) ya que solo hay definidos 151 de ellos y se utilizan 105.

Los cases del swich son los siguientes y a cada uno le corresponde un opcode:

| ADC | 0x69 0x6D 0x7D 0x69 |

PHA | 0x48 |

| AND | 0x29 0x2d 0x3D 0x39 |

PHP | 0x08 |

| ASL | 0x0A 0x0E 0x1E |

PLA | 0x68 |

| Branch | 0x90 0xB0 0xF0 0x30 0xD0 0x10 |

PLP | 0x28 |

| Clear | 0x18 0xB8 |

ROL | 0x2A 0x2E 0x3E |

| CMP | 0xC9 0xCD 0xDD 0xD9 0xE0 0xEC 0xC0 0xCC |

ROR | 0x6A 0x6E 0x7E |

| DEC | 0xCE 0xDE 0xCA 0x88 |

SBC | 0xE9 0xED 0xFD 0xF9 |

| DEX DEY |

0xCA 0x88 |

SEC | 0x38 0xF8 0x78 |

| EOR | 0x49 0x4D 0x5D 0x59 |

STA | 0x8D 0x9D 0x99 |

| INC | 0xEE 0xFE |

STX STY |

0x8E 0x8C |

| INX INY |

0xE8 0xC8 |

TAX TAY |

0xAA 0xA8 |

| JMP | 0x4C | TXA TYA |

0x8A 0x98 |

| JSR | 0x20 | TXS TSX |

0x9A 0xBA |

| LDX | 0xA2 0xAE 0xBE |

LDA | 0xA9 0xAD 0xBD 0xB9 |

| LDY | 0xA0 0xAC 0xBC |

LSR | 0x4A 0x4E 0x5E |

| ORA | 0x09 0x0D 0x1D 0x19 |

RTS | 0x60 |

Se definieron banderas como constantes:

| NFLAG | 0x80 | 10000000 | Bandera de negativo |

| VFLAG | 0x40 | 01000000 | Bandera de overflow |

| DFLAG | 0x08 | 00001000 | Bandera de modo decimal |

| IFLAG | 0x04 | 00000100 | Bandera de interrupt |

| VFLAG | 0x02 | 00000010 | Bandera de cero |

| CFLAG | 0x01 | 00000001 | Bandera de carry |

Enlaces externos

- MOS 6510 datasheet (formato GIF, zip)

- MOS 6510 datasheet (formato PDF)

- MOS 6510 datasheet (Nov. 1982, formato PDF)

- Emulador MOS 6510 creado por Angélica Partida Hanon

Atribución

Este artículo proviene originalmente de Wikipedia y por ello no sigue la licencia general del site, sino la

|

GFDL: Se autoriza la copia, la distribución y la modificación de este documento bajo los términos de la licencia de documentación libre GNU, versión 1.2 o cualquier otra que posteriormente publique la Fundación del Software Libre (Free Software Fundation); sin secciones invariables (Unvariant Sections), textos de portada (Front-Cover Texts), ni textos de contraportada (Back-Cover Texts).

Se incluye una copia en inglés de esta licencia en el artículo "GNU Free Documentation License". |

|