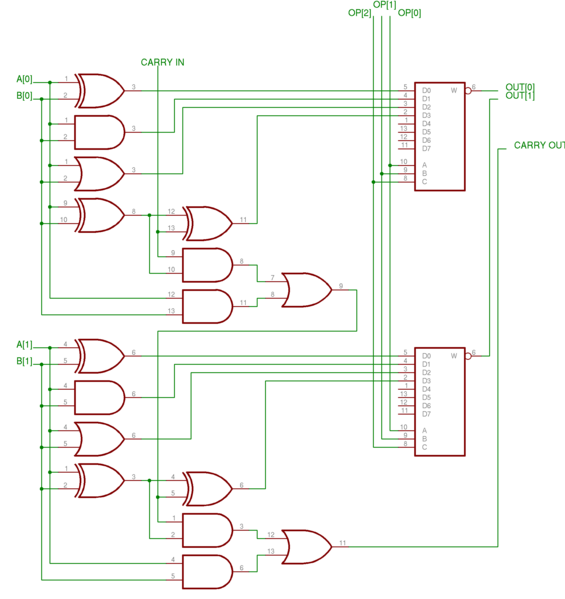

Archivo:2-bit ALU.png

Archivo original (2042 × 2166 píxeles; tamaño de archivo: 51 kB; tipo MIME: image/png)

- en: A simple example arithmetic logic unit (ALU) that does AND, OR, XOR, and addition.

- es: Una ALU simple de 2 bits que hace operaciones de AND, OR, XOR y adición

Procedencia

Imagen subida a Commons obra de Cburnett

Licencia

|

GFDL: Se autoriza la copia, la distribución y la modificación de este documento bajo los términos de la licencia de documentación libre GNU, versión 1.2 o cualquier otra que posteriormente publique la Fundación del Software Libre (Free Software Fundation); sin secciones invariables (Unvariant Sections), textos de portada (Front-Cover Texts), ni textos de contraportada (Back-Cover Texts).

Se incluye una copia en inglés de esta licencia en el artículo "GNU Free Documentation License". |

EN

This ALU is a 2-bit ALU with two inputs (operands) named A and B: A[0] & B[0] is the least-significant bit and A[1] & B[1] is the most-significant bit

Each bit of this ALU is identical with the exception of the handling of the carry bit. The handling of one bit is explained below.

The A & B inputs lead into the four gates on the left (from top to bottom): XOR, AND, OR, and XOR. The top three gates perform XOR, AND, and OR operations on A & B. The last gate is the initial gate into a full adder.

The final step to each bit is the multiplexer at the end. The 3-bit OP input (from the control unit) determines which of the functions is outputted:

- OP = 000 → XOR

- OP = 001 → AND

- OP = 010 → OR

- OP = 011 → Addition

Clearly, the last four inputs of the multiplexer are free for other functions (subtraction, multiplication, division, NOT A, NOT B, etc.). Although OP[2] is not currently used (though it is included and connected), it will be needed in order to use more than the 4 operations listed above.

The carry in and carry out are typically connected to some form of a status register.

ES

Esta ALU es una ALU de 2-bit con dos entradas (operandos) llamadas A y B: A[0] & B[0] corresponden al bit menos significativo y A[1] & B[1] corresponden al bit más significativo.

Cada bit de esta ALU es idéntico con la excepción del direccionamiento del carry bit. El manejo de este bit es explicado más adelante.

Las entradas A & B van ubicadas hacia las cuatro compuertas de la izquierda (de tope a fondo): XOR, AND, OR, y XOR. Las tres primeras compuertas realizan las operaciones XOR, AND, y OR sobre los datos A & B. La última compuerta es la compuerta inicial de un sumador completo.

El paso final de las operaciones sobre cada bit es la multiplexación de los datos. La entrada OP de 3-bit (de la unidad de control) determina cual de las funciones se van a realizar:

- OP = 000 → XOR

- OP = 001 → AND

- OP = 010 → OR

- OP = 011 → Adición

Claramente se ve que las otras cuatro entradas del multiplexor están libres para otras operaciones (subtracción, multiplicación, división, NOT A, NOT B, etc.). Aunque OP[2] no es usada en este montaje (a pesar de estar incluída y conectada), ésta sería usada en el momento de realizar otras operaciones además de las 4 operaciones listadas arriba.

Los datos de carry de entrada y carry de salida normalmente van conectados a algún tipo de registro de estado.

Historial del archivo

Haz clic sobre una fecha y hora para ver el archivo tal como apareció en ese momento.

| Fecha y hora | Miniatura | Dimensiones | Usuario | Comentario | |

|---|---|---|---|---|---|

| actual | 21:25 20 jun 2007 |  | 2042 × 2166 (51 kB) | Museo8bits (discusión | contribs.) | *'''en:''' A simple example arithmetic logic unit (ALU) that does AND, OR, XOR, and addition. *'''es:''' Una ALU simple de 2 bits que hace operaciones de AND, OR, XOR y adición {{img_commons|2-bit_ALU.png|Cburnett|Cburnett|GFDL}} ===EN=== This ALU is a |

No puedes sobrescribir este archivo.

Usos del archivo

La siguiente página usa este archivo: