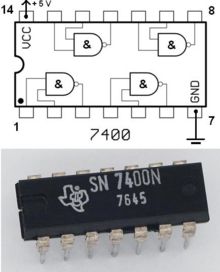

Serie 7400

Por serie 7400 se conoce a los circuitos digitales integrados de tecnología TTL (lógica transistor-transistor o en inglés transistor-transistor logic), que forman una subfamilia de semiconductores, dentro del campo de la electricidad y la electrónica.

El material empleado para su construcción más común es el silicio, y el componente básico en estos circuitos es el transistor bipolar. Las características destacables de estos componentes son las siguientes:

- Tensión de alimentación: 5 V, con una tolerancia (de 4,5 V a 5,5 V).

- Niveles lógicos: entre 0,2 V y 0,8 V para el nivel bajo (L) y entre 2,4 V y 5 V para el nivel alto (H), ya que estos chips son activados por altos y bajos, o también llamados 0 y 1, dígitos del sistema binario utilizados para estos usos en la electrónica.

- Código identificador: el 74 para los comercialesy el 54 para los de diseño militar. Estos últimos son chips más desarrollados, ya que los de serie 74 soportan menos rangos de temperaturas.

- Temperatura de trabajo: de 0 °C a 70 °C para la serie 74 y de -55º hasta los 125 °C para la 54.

Las demás características dependen de la subfamilia que se utilice, podemos encontrarnos con chips de modelo estándar, de bajo consumo (L), de alta velocidad (H), Schottky (S), Schottky de bajo consumo (LS), Schottky avanzado (AS), TTL Schottky avanzado de bajo consumo (ALS), ó el TTL rápido (TTL ALS Fairchild) (F) entre otos.

Centrándonos en el modelo estándar podemos sobre éste modelo que su retraso es de 10 ns siendo el de menor retraso el modelo Schottky (3ns) y el de mayor el modelo de bajo consumo (33 ns). El consumo por puerta es de 10 mW siendo el menor el de bajo consumo de 1mW y el de mayor consumo el de alta velocidad de 22 mW, la velocidad en el estándar es de 35 MHz siendo la menor en el de bajo consumo de 3 MHz y mayor en el Schottky de 125 MHz, el margen de ruido para el modelo estándar que veremos a continuación, es de 0,4V siendo más distante y variable en el modelo LS, de 0,7 V para el nivel lógico 1 y de 0,3 V para el nivel lógico 0: Por último el abanico de salida es de 10 para el estándar y el de alta velocidad y de 20 para el resto.

La utilización de éstos chips es muy amplia ya que alojan en su interior multitud de componentes electrónicos para distintas aplicaciones. Podemos encontrar circuitos de la serie 74 con puertas lógicas, Buffers, biestables, circuitos aritméticos, como semisumador, sumador completo, sumador paralelo, sistemas combinacionales o secuenciales entre otros.

Atribución

Este artículo proviene originalmente de Wikipedia y por ello no sigue la licencia general del site, sino la

|

GFDL: Se autoriza la copia, la distribución y la modificación de este documento bajo los términos de la licencia de documentación libre GNU, versión 1.2 o cualquier otra que posteriormente publique la Fundación del Software Libre (Free Software Fundation); sin secciones invariables (Unvariant Sections), textos de portada (Front-Cover Texts), ni textos de contraportada (Back-Cover Texts).

Se incluye una copia en inglés de esta licencia en el artículo "GNU Free Documentation License". |

|