Intel Itanium

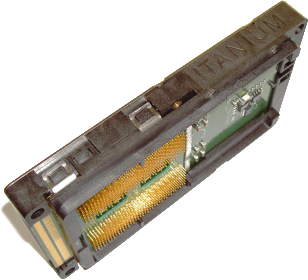

El Itanium, también conocido por su nombre en código Merced, fue el primer microprocesador de la arquitectura Intel Itanium (antes llamada IA64, creada por Hewlett-Packard y desarrollada conjuntamente por HP e Intel) que Intel lanzó al mercado. Aunque su lanzamiento inicialmente se planeó para 1998, no se produjo hasta mayo de 2001.

Este procesador se fabricaba utilizando un proceso de 180 nm y disponía de 32 KB de memoria caché de primer nivel (16 para datos y 16 para instrucciones), 96 KB de caché de segundo nivel integrada en el núcleo y 2 ó 4 MB de caché de tercer nivel exterior al núcleo. Estaba disponible en versiones a 733 u 800 MHz.

La arquitectura del Itanium se diferencia drásticamente de las arquitecturas x86 y x86-64 usadas en otros procesadores de Intel. La arquitectura se basa en un explícito paralelismo a nivel de instrucción, con el compilador tomando decisiones sobre que instrucciones deben ejecutarse en paralelo. Este acercamiento permite que el procesador ejecute hasta seis instrucciones por ciclo de reloj. A diferencia de otras arquitecturas superescalares, Itanium no precisa de hardware elaborado para seguir l a pista de de las dependencias de las instrucciones durante la ejecución paralela.

En el momento de su lanzamiento (Junio de 2001), Itanium no era superior a los microprocesadores contemporáneos RISC y CISC. Compitió por el segmento bajo del mercado (de 4 CPUs para abajo) con los servidores basados en los procesadores x86, y en le segmento alto con las arquitecturas IBM POWER y Sun SPARC.

Intel reposiciona al Itanium para concentrarse en la gama alta y los ordenadores HPC, intentando duplicar el acertado esquema de mercado horizontal de los x86 (una sola arquitectura, múltiples vendedores de sistemas). Su éxito se limita a reemplazar a los sistemas PA-RISC y Alpha de HP y a los MIPS en los HPC de Silicon Graphics. POWER y SPARC permanecen fuertes, mientras que la arquitectura x86 de 32 bits crece en el espacio empresarial. Con las economías de escala alimentadas por su enorme base instalada, x86 es la arquitectura horizontal preeminente en el mercado empresarial. Intel y HP reconocen que Itanium no es competitivo y lo reemplazan por el Itanium 2 un año antes de lo planeado, en 2002. Solamente algunos miles de los Itanium se vendieron, debido a la disponibilidad limitada causada por baja producción, relativamente pobre rendimiento y alto coste. Sin embargo, esas máquinas eran útiles para desarrollar software para los Itanium 2. IBM creó un supercomputador basado en este procesador.<ref name="Thunder">Plantilla:Cite web</ref>

| Nombre en código | proceso | lanzamiento | Frecuencia | Cache L2/ core |

Cache L3/ core |

Bus | dies/ dispositivo |

cores/ die |

Vatios/ dispositivo |

comentarios |

|---|---|---|---|---|---|---|---|---|---|---|

| Itanium | ||||||||||

| Merced | 180 nm | Junio de 2001 | 733 MHz | 96 KiB | 3 MiB* | 133 MHz | 1 | 1 | ? | caché L3 situada fuera de un die |

| 180 nm | Junio de 2001 | 900 MHz | 96 KiB | 4 MiB* | 133 MHz | 1 | 1 | ? | ||

Referencias

Atribución

Este artículo proviene originalmente de Wikipedia y por ello no sigue la licencia general del site, sino la

|

GFDL: Se autoriza la copia, la distribución y la modificación de este documento bajo los términos de la licencia de documentación libre GNU, versión 1.2 o cualquier otra que posteriormente publique la Fundación del Software Libre (Free Software Fundation); sin secciones invariables (Unvariant Sections), textos de portada (Front-Cover Texts), ni textos de contraportada (Back-Cover Texts).

Se incluye una copia en inglés de esta licencia en el artículo "GNU Free Documentation License". |

|